#### Università di Pisa Dipartimento di Informatica

Dottorato di Ricerca in Informatica

Ph.D. Thesis: TD-09/03

### Dynamic shared data in structured parallel programming frameworks

Marco Aldinucci

December 2003

Address: Via F. Buonarroti 2, 56127 Pisa - Italy Tel: +39-050-2212728 — Fax: +39-050-2212726 E-mail: aldinuc@di.unipi.it — Web page: http://www.di.unipi.it/~aldinuc Thesis Supervisors: Prof. Marco Vanneschi, Prof. Marco Danelutto

### Abstract

This work originates from the wish to simplify the coding of irregular applications within structured parallel programming environments. In these environments parallelism is exploited by composing "skeletons", i.e. parallelism exploitation patterns. The skeletal approach has been proved to be effective, at least if application algorithms can be somehow expressed in terms of skeleton composition. However, in some cases our skeletal frameworks fail in providing the application programmer with convincing solutions both from ease of programming and performance viewpoints. Major lacks of expressivity have emerged in dynamic/irregular algorithms and applications that oddly access to large data sets. The first part of the thesis moves along this path, and reports all attempts we made to improve the effectiveness of environments' compiler, static optimizer, and run-time support.

The main goal of the thesis is to take a step further with respect to the achieved results. In particular we aim to defeat expressivity lacks emerged in skeletal languages approaching irregular problems and dealing with dynamic data structures. The basic idea consists in providing the application designer with a shared address space and a skeletal framework that enables and enforces the co-design of (shared) dynamic data structures and (parallel) algorithms.

At this aim, a new skeletal programming environment based on shared address programming is proposed (i.e. eskimo). The language is as an extension of a "host" language (i.e. the C language). eskimo is conceived to be a framework to experiment how to support dynamic data structures in a skeletal framework. Its run-time support is based on a software distributed shared memory, and allows the programmer to freely access data items in the shared memory. eskimo is designed to match the hooks offered by ASSIST, thus to be experimented within. Notably eskimo is not yet another DSM, rather it relies on DSM already known technologies to experiment the co-design of dynamic data structures and parallel programming patterns enforcing locality in the distributed memory access.

eskimo has been designed and developed from scratch. eskimo run-time support exploits multithreading, dynamic data-driven scheduling, and is very tolerant with respect to standard POSIX programming framework. It will be released as open source package.

To Rosalia

Oscuramente, credette di intuire che il passato è la sostanza di cui è fatto il tempo; perciò questo diviene subito passato.

Jorge Luis Borges, El Aleph, 1952.

'You were quite entitled to make any suggestion or protest at the appropriate time, you known ... the plans have been available in the local planning office for the last nine months.'

'Oh yes, well as soon as I heard I went straight round to see them, yesterday afternoon. You hadn't exactly gone out of your way to call attention to them, had you? I mean like actually telling anybody or anything.'

'But the plans were on display  $\dots$ '

'On display? I eventually had to go down to the cellar to find them.'

'That's the display department.'

'With a torch.'

'Ah, well the lights had probably gone.'

'So had the stairs.'

'But look, you found the notice, didn't you?'

'Yes, I did. It was on display in the bottom of a locked filing cabinet stuck in a disused lavatory with a sign on the door saying *Beware of the Leopard*.'

Douglas Adams, The Hitchhiker's Guide to the Galaxy, 1979.

### Acknowledgments

A huge word of gratitude is owed to my supervisors Marco Vanneschi and Marco Danelutto. Both of them supported me far beyond I have expected, and actually they was the *deus ex machina* of my scientific experience. I hope to acquire their competence, and in particular their capacity to discern the real core of problems by throwing away in real time all misleading details.

I also took full advantage from my participation to several projects, which offered me the opportunity of meeting and discussing with many people. In particular I would remember Susanna Pelagatti, Sergei Gorlatch and Christian Lengauer.

I would like to acknowledge many of the persons I met in these years. My housemate Valentina Von Vivaldi who stayed awake up to improbable hours of the night trying to improve my English (almost uselessly). My room-mates at the department Nadia and Valentina who kindly tolerated my loudly arguing against the monitor while using the debugging tools (gdb, screwdriver, hammer, ...). Stefano from the Aguaraja kayak club; he taught me the eskimo technique and the importance of being self-confident (it may happen to be useful when you are sit upside-down in the middle of a creek, and sometimes also in research).

I also deserve my gratitude to the many people who shared with me the work, the spare time and the aperitifs. Amongst them Andrea, with whom I have many discussion about computer science, life, universe and anything (proudly, we hardly agree on anything). Emilio and Francesco who are able to drink more aperitfs than me (not an easy task).

Non posso dimenticare di ringraziare la mia famiglia: babbo Silvano e mamma Laura che non hanno ancora ben capito – non per loro colpa – che lavoro io faccia *di preciso*; mio fratello Piero, che oltre ad essere diventato un brillante informatico, ha assolto anche ai miei doveri familiari. Non so come, ma siete riusciti a lasciarmi vivere la mia vita pur essendomi sempre vicini.

Infine un pensiero per Rosalia. La sua naturale empatia ha reso il lavoro meno pesante; la sua spensieratezza la vita più felice. Un pensiero per i nostri viaggi in moto con il caldo e con il freddo, per il blu del mare ed il rosso del tramonto di San Vito ... un pensiero per tutto quello che ancora deve venire.

## Contents

| 1        | Intr | oduction                                                                                      | 1  |

|----------|------|-----------------------------------------------------------------------------------------------|----|

|          | 1.1  | Contributes and motivations of the thesis                                                     | 2  |

|          | 1.2  | Technical background                                                                          | 4  |

|          |      | 1.2.1 Parallel architectures: programming model                                               | 8  |

|          |      | 1.2.2 High-level parallel programming                                                         | 10 |

|          | 1.3  | A deeper look at framework and motivations                                                    | 15 |

|          |      | 1.3.1 eskimo motivations                                                                      | 16 |

|          |      | 1.3.2 eskimo features                                                                         | 17 |

|          | 1.4  | Plan of the thesis                                                                            | 18 |

| <b>2</b> | Stru | ctured parallel programming 2                                                                 | 23 |

|          | 2.1  |                                                                                               | 28 |

|          | 2.2  | 1                                                                                             | 33 |

|          |      |                                                                                               | 33 |

|          |      |                                                                                               | 38 |

|          |      | 2.2.3 Tool architecture and implementation $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 43 |

|          |      |                                                                                               | 45 |

|          | 2.3  | Exploiting efficient skeletons in Java                                                        | 54 |

|          |      | 2.3.1 Lithium skeletons                                                                       | 55 |

|          |      | 2.3.2 Skeleton optimizations                                                                  | 59 |

|          |      | 2.3.3 Lithium API                                                                             | 60 |

|          |      | 2.3.4 Lithium implementation                                                                  | 63 |

|          |      | 2.3.5 Experiments $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$     | 64 |

|          | 2.4  | The ASSIST programming environment                                                            | 73 |

|          |      | 2.4.1 Motivations and main goals                                                              | 73 |

|          |      | 2.4.2 Features of ASSIST                                                                      | 75 |

|          |      | 2.4.3 Structure of ASSIST programs                                                            | 76 |

|          |      | 2.4.4 Parallel module                                                                         | 77 |

| 3        | DSI  | I: the state of the art                                                                       | 31 |

|          | 3.1  | Basic concepts                                                                                | 81 |

|          |      | 3.1.1 Cache coherence                                                                         | 83 |

|          |      | 3.1.2 Memory consistency                                                                      | 83 |

|          |      | 3.1.3 Characterizing DSMs                                                                                                                       |

|----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 3.2  | Implementation level                                                                                                                            |

|          |      | 3.2.1 Hardware                                                                                                                                  |

|          |      | 3.2.2 Software                                                                                                                                  |

|          |      | 3.2.3 Hybrid                                                                                                                                    |

|          | 3.3  | Memory consistency models                                                                                                                       |

|          |      | 3.3.1 Sequential consistency                                                                                                                    |

|          |      | 3.3.2 Relaxed consistency models                                                                                                                |

|          |      | 3.3.3 Multi-protocol consistency                                                                                                                |

|          | 3.4  | Data replication                                                                                                                                |

|          | 3.5  | Software implementation issues                                                                                                                  |

|          | 3.6  | Athapascan                                                                                                                                      |

| 4        | eski | mo: design principles 111                                                                                                                       |

|          | 4.1  | eskimo: A new skeletal language                                                                                                                 |

|          |      | 4.1.1 Exploiting parallelism in eskimo                                                                                                          |

|          |      | 4.1.2 Concurrency and flows of control                                                                                                          |

|          |      | 4.1.3 Sharing memory among flows of control                                                                                                     |

|          |      | 4.1.4 Reading and Writing Shared Variables                                                                                                      |

|          | 4.2  | Skeletons and their expected pay-back                                                                                                           |

|          | 4.3  | Related work and discussion                                                                                                                     |

| <b>5</b> | eski | mo: language usage 127                                                                                                                          |

|          | 5.1  | eskimo computation model                                                                                                                        |

|          | 5.2  | eskimo language                                                                                                                                 |

|          |      | 5.2.1 Writing and running eskimo programs                                                                                                       |

|          |      | 5.2.2 Types and variables $\ldots \ldots 133$ |

|          |      | 5.2.3 Exploiting parallelism                                                                                                                    |

|          | 5.3  | A running example                                                                                                                               |

| 6        | eski | mo: implementation 149                                                                                                                          |

|          | 6.1  | Abstracting the architecture                                                                                                                    |

|          |      | 6.1.1 A multithreaded support                                                                                                                   |

|          |      | 6.1.2 eskimo Shared Virtual Memory                                                                                                              |

|          | 6.2  | Shared Data Types                                                                                                                               |

| 7        | eski | mo: experiments 167                                                                                                                             |

|          | 7.1  | Building and visiting a tree                                                                                                                    |

|          | 7.2  | N-body Barnes-Hut algorithm                                                                                                                     |

|          |      | 7.2.1 Barnes-Hut experiments                                                                                                                    |

| 8 | Dise                 | cussion and concluding remarks | 181 |

|---|----------------------|--------------------------------|-----|

|   | 8.1                  | Assessments                    | 182 |

|   | 8.2                  | Discussion                     | 182 |

|   | 8.3                  | Future works                   | 185 |

|   | 8.4                  | The ASSIST perspective         | 186 |

|   | $\operatorname{Bib}$ | liography                      | 189 |

# List of Figures

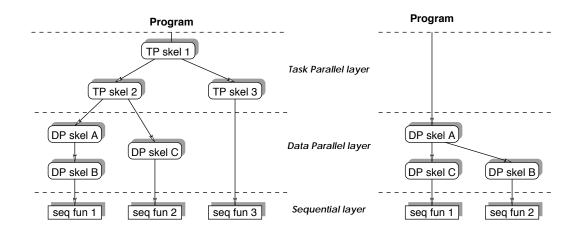

| $1.1 \\ 1.2$ | Fraction of transistors on microprocessor chip devoted to caches<br>Typical parallel machine schemes                                                                                                       | 79       |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

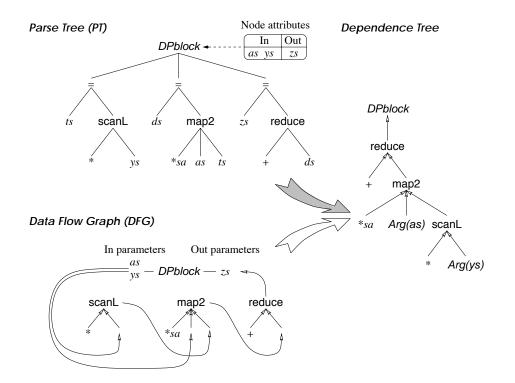

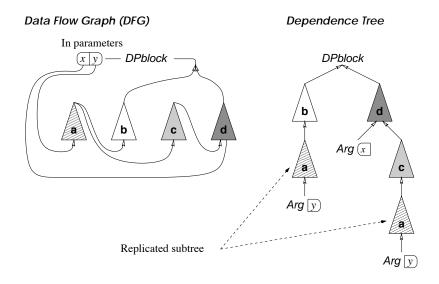

| $2.1 \\ 2.2$ | Three-tier applications: two correct skeleton calling schemes<br>The parse tree, the data flow graph and the dependence tree of polynomial evaluation. Skel-BSP skeletons are in serif font. Special nodes | 34       |

| 2.3          | are in <i>slanted serif</i> font. Sequential functions are in <i>italic</i> font<br>Replicating shared trees. Each triangle stands for a tree representing                                                 | 39       |

| 9.4          | a TL expression.                                                                                                                                                                                           | 41       |

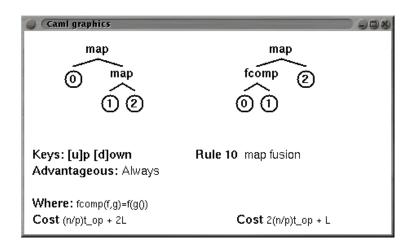

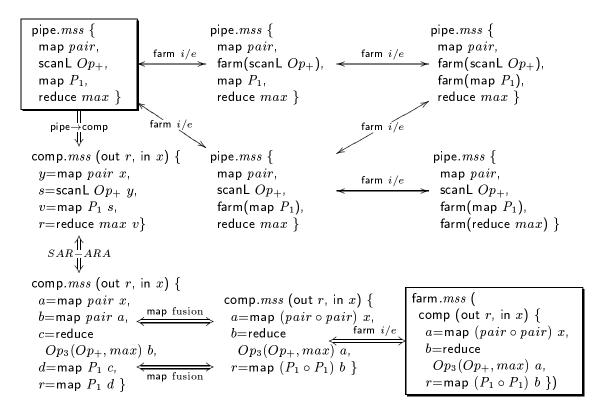

| 2.4          | Internal representation of rule map fusion, conditions of its applica-<br>bility and performance of the two sides of the rule.                                                                             | 42       |

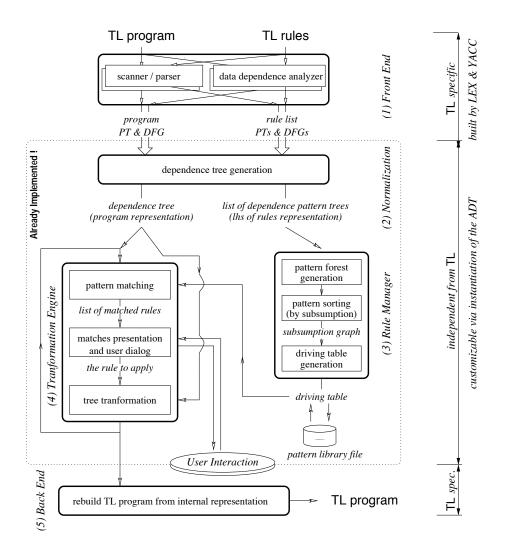

| 2.5          | Global structure of the Meta transformation system                                                                                                                                                         | 44       |

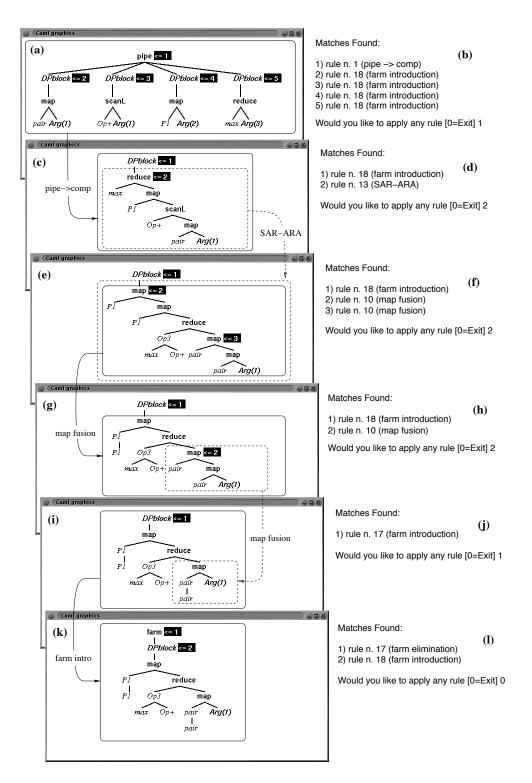

| 2.6          | Transformation of the MSS program using the Meta tool. Skel-BSP                                                                                                                                            |          |

|              | skeletons are in serif font. Special nodes are in <i>slanted serif</i> font.                                                                                                                               |          |

|              | Sequential functions are in <i>italic</i> font                                                                                                                                                             | 46       |

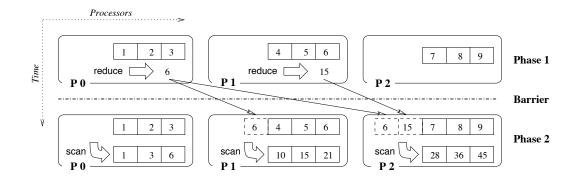

| 2.7          | Two-phase BSP parallel prefix (TPscanL) using + as global operation.                                                                                                                                       | 49       |

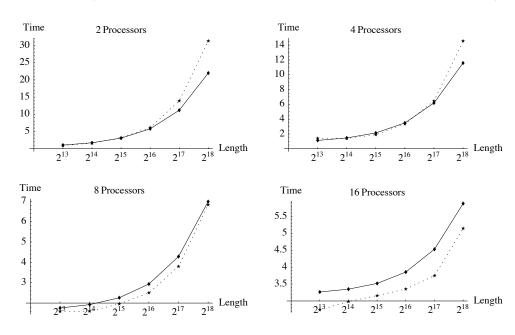

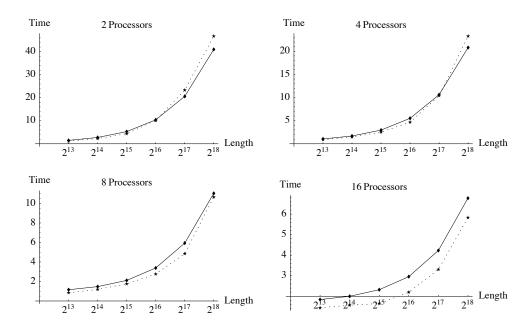

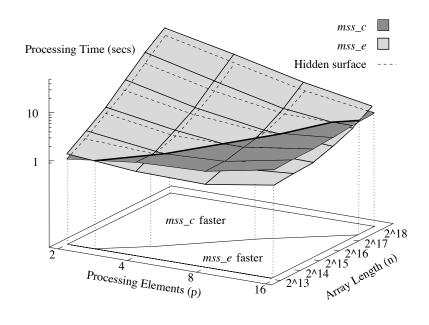

| 2.8          | a) mss_c and b) mss_e: Comparing predicted performance (solid                                                                                                                                              |          |

|              | lines) with experimental performance (dotted lines). Each experiment                                                                                                                                       |          |

|              | is performed on several array lengths (x-axis). Four different cluster                                                                                                                                     |          |

|              | configurations are experimental $(2,4,8,16 \text{ processors})$                                                                                                                                            | 52       |

| 2.9          | Experimental performance of ${\bf mss\_c}$ and ${\bf mss\_e}$ programs on several                                                                                                                          |          |

|              | cluster configurations and several array lengths                                                                                                                                                           | 53       |

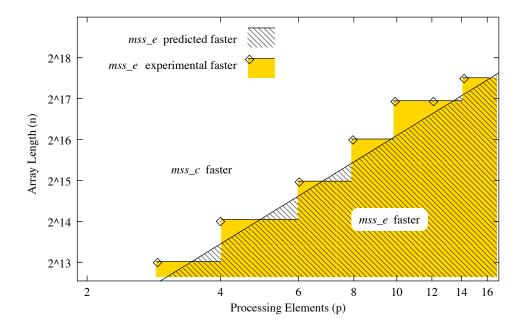

| 2.10         | I (                                                                                                                                                                                                        |          |

|              | than <b>mss_c</b> when SAR-ARA is advantageous)                                                                                                                                                            | 53       |

| 2.11         | Lithium operational semantic. x, $y \in \text{Value}; \sigma, \tau \in \text{Value}^*; \ell, \ell_i, \ldots \in$                                                                                           | •        |

| 0.10         | Label = Strings $\cup \{\bot\}; \mathcal{O}: Label \times Value \rightarrow Label. \dots$                                                                                                                  | 56       |

|              | Stream label usage examples.                                                                                                                                                                               | 56       |

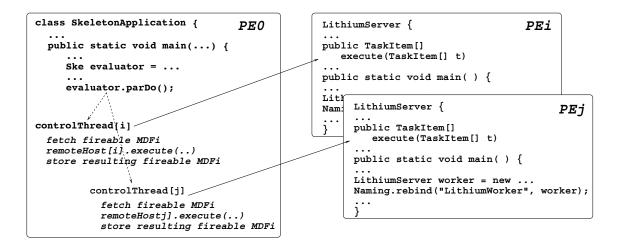

| 2.13         | Sample Lithium code: parallel application exploiting task farm paral-                                                                                                                                      | 01       |

| 0.14         | lelism.                                                                                                                                                                                                    | 61       |

|              | Lithium architecture.                                                                                                                                                                                      | 62       |

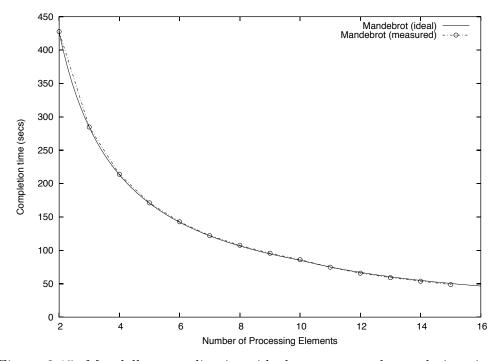

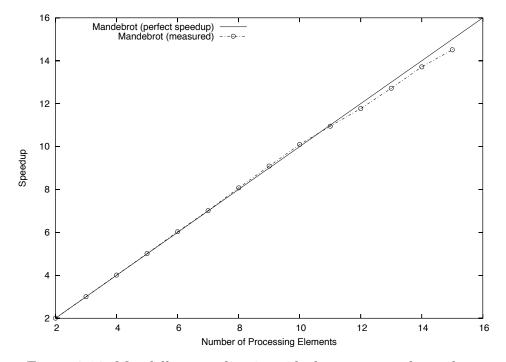

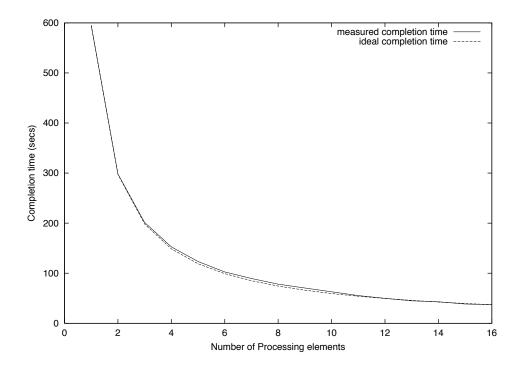

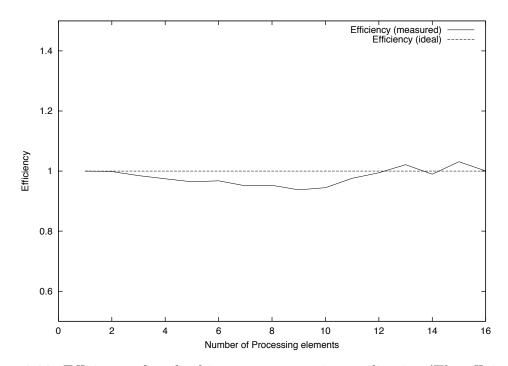

|              | Mandelbrot application: ideal vs. measured completion time                                                                                                                                                 | 65<br>65 |

|              | Mandelbrot application: ideal vs. measured speedup                                                                                                                                                         | 65       |

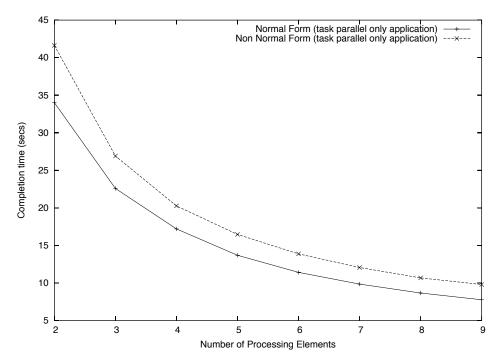

| 2.1(         | "Synthetic" task parallel application: Normal vs. non normal form                                                                                                                                          | 66       |

|              | completion times                                                                                                                                                                                           | 00       |

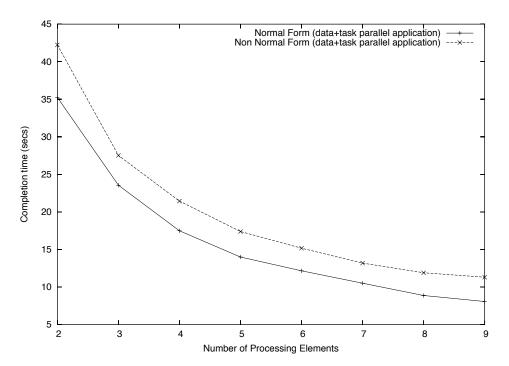

| 2.18  | "Synthetic" task+data parallel application: Normal vs. non normal form completion times                                 |

|-------|-------------------------------------------------------------------------------------------------------------------------|

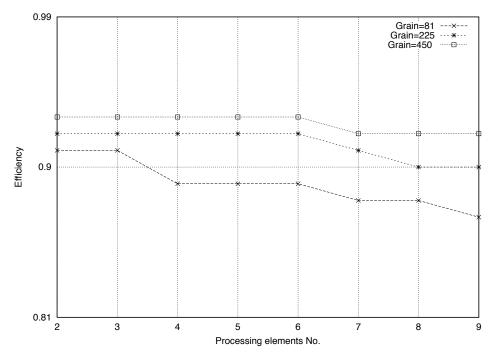

| 2 1 9 | Effect of grain on efficiency                                                                                           |

|       | Medical image segmentation application: screen snapshot 68                                                              |

|       | Results with the medical image segmentation application                                                                 |

|       | Efficiency of medical image segmentation application (The efficiency                                                    |

| 2.22  | is figured out with respect to the sequential execution time computed<br>on the slower processors ( $PE \in [1, 10]$ )) |

| 2.23  | Load balancing on heterogeneous processing elements (100 tasks) 70                                                      |

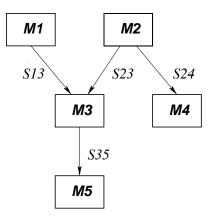

|       | Medical image processing application skeleton                                                                           |

|       | An ASSIST graph                                                                                                         |

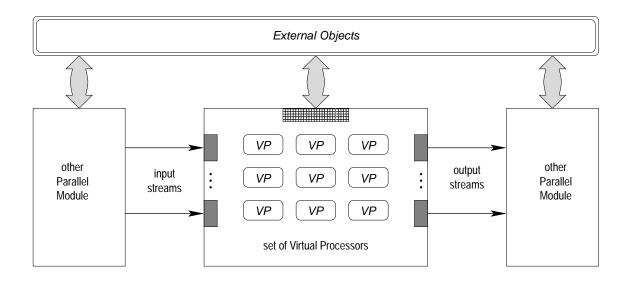

|       | Graphical scheme of a Parallel Module                                                                                   |

|       |                                                                                                                         |

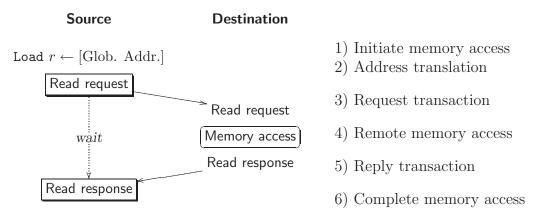

| 3.1   | Shared address space abstraction:two-way request-response protocol 82                                                   |

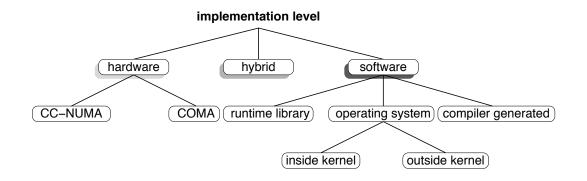

| 3.2   | DSM implementation level taxonomy                                                                                       |

| 3.3   | Abstraction of the memory subsystem under the sequential consis-                                                        |

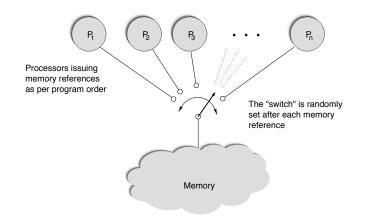

|       | tency model                                                                                                             |

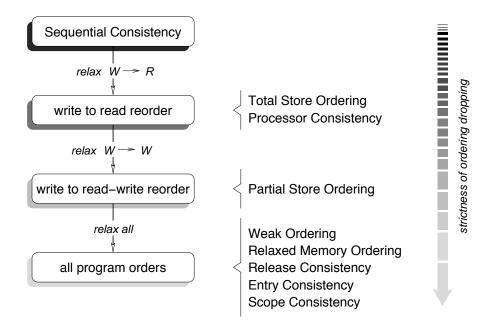

| 3.4   | Relaxation relations among various system specification 91                                                              |

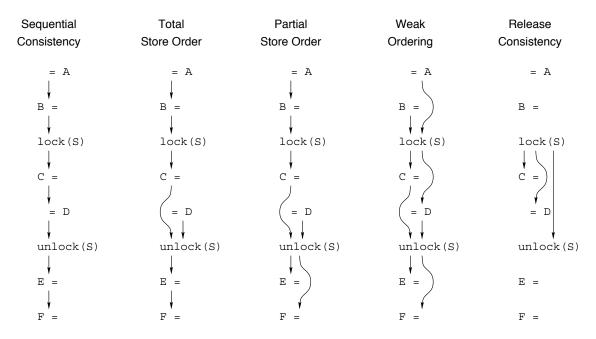

| 3.5   | Orders imposed in a program by various consistency models. An                                                           |

|       | arrow show a mandatory order, arrows' transitive closure show the                                                       |

|       | partial order among the instructions                                                                                    |

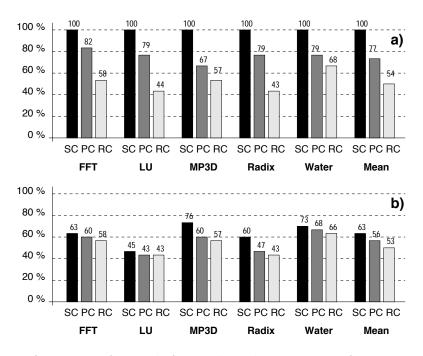

| 3.6   | Performance of straightforward implementation of memory consis-                                                         |

|       | tency models versus speculative out-of-order implementation. (Per-                                                      |

|       | formance figures taken from Adve et al. $[4]$ )                                                                         |

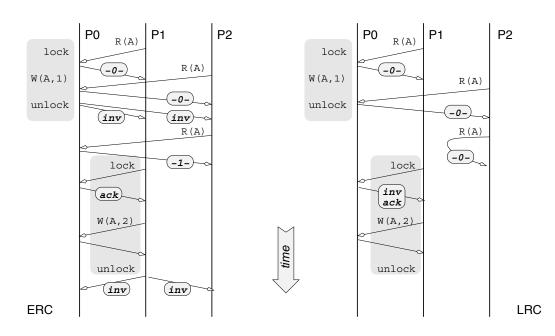

| 3.7   | Eager Release Consistency (ERC) and Lazy Release Consistency (LRC).                                                     |

|       | ERC propagate invalidations at release point, while LRC coalesces in-                                                   |

|       | validation with lock grant at acquire point                                                                             |

| 3.8   | An example highlighting differences between ERC and LRC program-                                                        |

|       | ming models                                                                                                             |

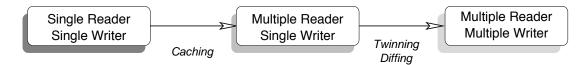

| 3.9   | DSM algorithms taxonomy                                                                                                 |

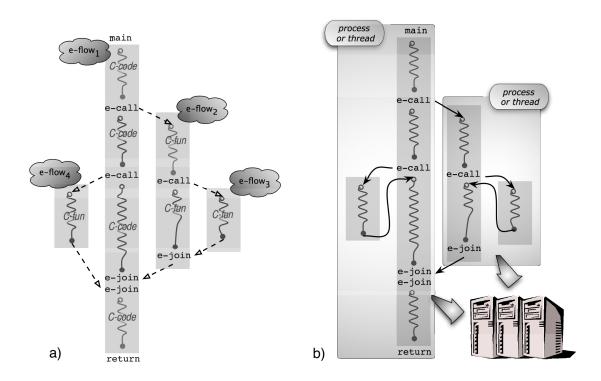

| 4.1   | An eskimo program execution intuitive view. a) Relationship among                                                       |

| 1.1   | e-calls, $e$ -joins and $e$ -flows (grey boxes). b) A possible execution of                                             |

|       | the program.                                                                                                            |

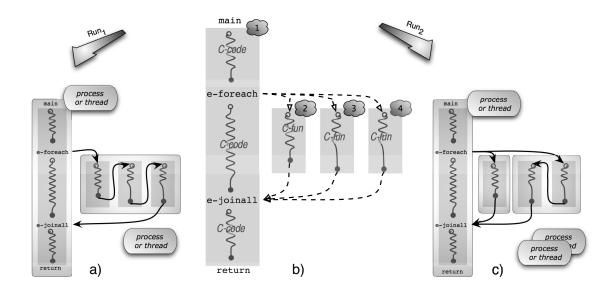

| 4.2   | An eskimo program resulting in different mapping and scheduling in                                                      |

| 1.2   | different runs                                                                                                          |

|       |                                                                                                                         |

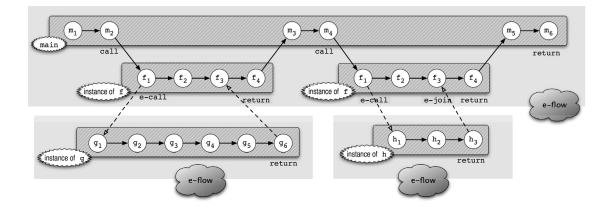

| 5.1   | An eskimo computation described by the <i>e-flow</i> graph. Dashed ar-                                                  |

|       | rows highlight <i>e-calls/e-joins</i> and solid arrows highlight standard C                                             |

|       | function calls                                                                                                          |

| 5.2   | Writing, configuring, compiling and running an eskimo program 132                                                       |

| 5.3   | Reading and writing shared variables                                                                                    |

| 5.4   | A simple eskimo program                                                                                                 |

| $5.5 \\ 5.6$      | The main of <i>build and visit</i> eskimo program                                                                                                                                                                                                                                                                                                         |            |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| $5.7 \\ 5.8$      | gram)                                                                                                                                                                                                                                                                                                                                                     | 148        |

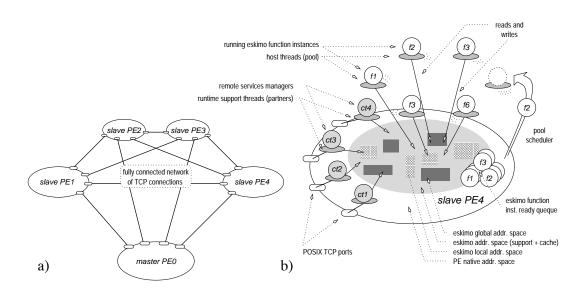

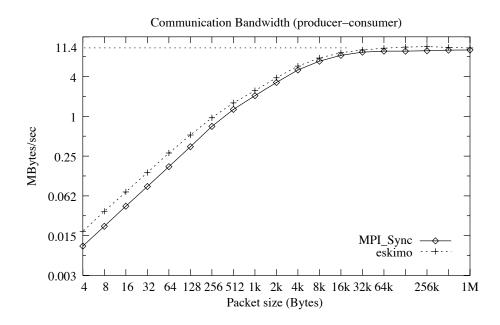

| 6.1<br>6.2        | a) Virtual architecture in the case of 5 PEs. b) PE internal organization <i>etier-0</i> communications performance for a producer-consumer pattern with respect to MPI communications on the backus cluster (2 PentiumII@266MHz, switched Ethernet 100MBit/sec). eskimo mimes the protocol shown in figure 3.1 for the write operation. MPI version uses |            |

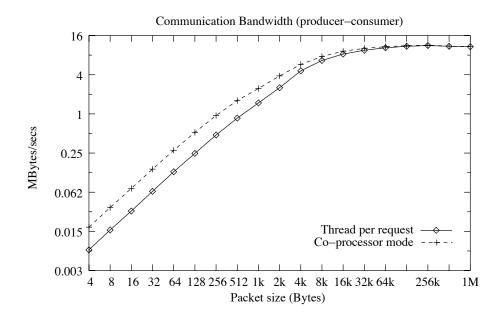

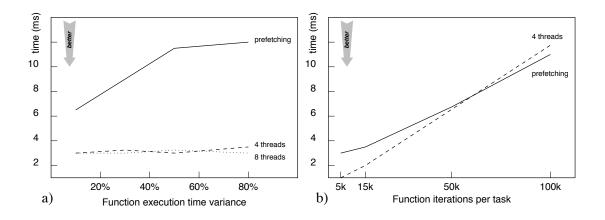

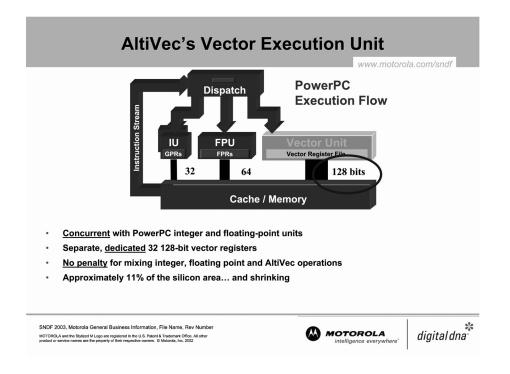

| 6.3               | MPI_Sync/MPI_Recv primitives                                                                                                                                                                                                                                                                                                                              |            |

| 6.4               | switched Ethernet 100MBit/sec)                                                                                                                                                                                                                                                                                                                            |            |

| 6.5               | Shared address implementation (eref_t): CRC part (in gray) is op-                                                                                                                                                                                                                                                                                         |            |

| 6.6<br>6.7<br>6.8 | tional and normally used only during debugging                                                                                                                                                                                                                                                                                                            | 159<br>161 |

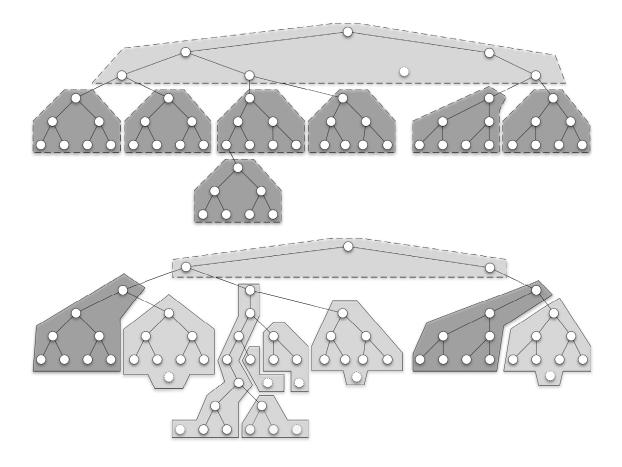

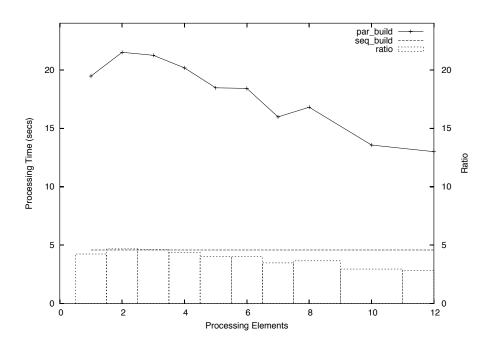

| 7.1               | Overhead in tree building versus #PEs on backus. Balanced binary tree (depth 22, 4M nodes, 48MBytes).                                                                                                                                                                                                                                                     | 169        |

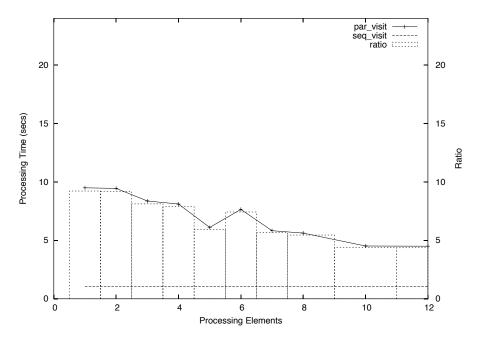

| 7.2<br>7.3        | Overhead in tree visiting versus #PEs on backus. Balanced binary tree (depth 22, 4M nodes, 48MBytes)                                                                                                                                                                                                                                                      |            |

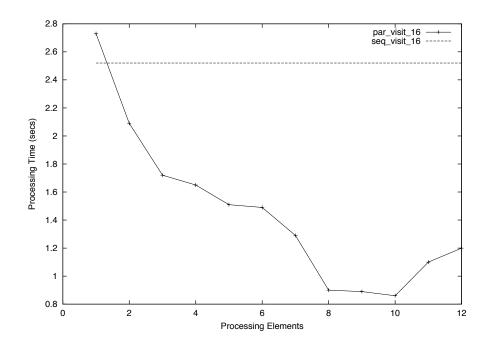

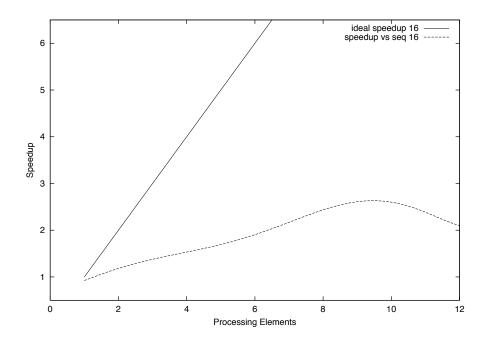

|                   | (depth 16, 64k nodes, 768 KBytes, 37 $\mu$ secs of computational load per node).                                                                                                                                                                                                                                                                          | 171        |

| 7.4               | Tree visiting speedup on backus. Balanced binary tree (depth 16, 64k nodes, 768 KBytes, 37 $\mu$ secs of computational load per node)                                                                                                                                                                                                                     | 171        |

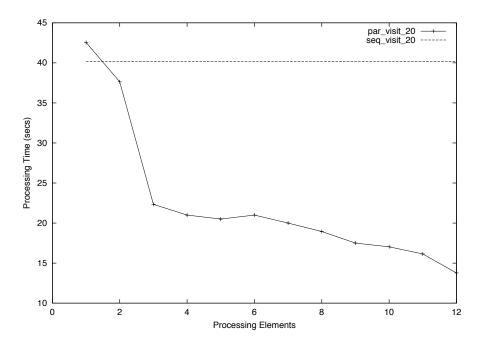

| 7.5               | Tree visit time versus $\#PEs$ on backus. Balanced binary tree (depth 20, 1M nodes, 12MBytes, 37 $\mu$ secs of computational load per node).                                                                                                                                                                                                              |            |

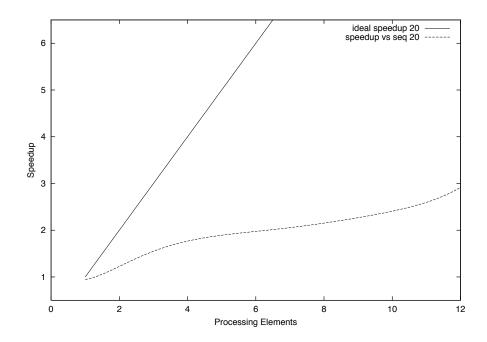

| 7.6               | Tree visiting speedup on backus. Balanced binary tree (depth 20,                                                                                                                                                                                                                                                                                          |            |

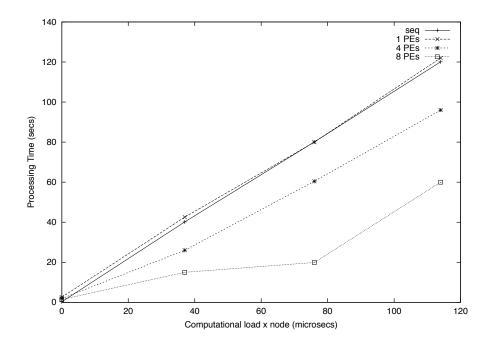

| 7.7               | 1M nodes, 12MBytes, 37 $\mu$ secs of computational load per node)<br>Tree visit time versus computational load on backus. Balanced bi-                                                                                                                                                                                                                    |            |

|                   | nary tree (depth 20, 1M nodes, 12MBytes)                                                                                                                                                                                                                                                                                                                  | 173        |

| 7.8  | Tree visiting overhead on a SMP cluster (2-way 550MHz PIII) 173               |  |  |  |

|------|-------------------------------------------------------------------------------|--|--|--|

| 7.9  | Tree visiting time, speedup and efficiency on a SMP cluster (2-way            |  |  |  |

|      | 550MHz PIII). Balanced binary tree (depth 18, 256k nodes, 3MBytes).174        |  |  |  |

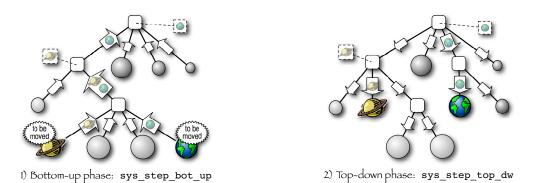

| 7.10 | A n-body system step in two phases (force calculation phase, in two           |  |  |  |

|      | sub-phases: bottom-up and top-down)                                           |  |  |  |

| 7.11 | eskimo pesudo-code of the bottom-up phase, see also Figure 7.10 175           |  |  |  |

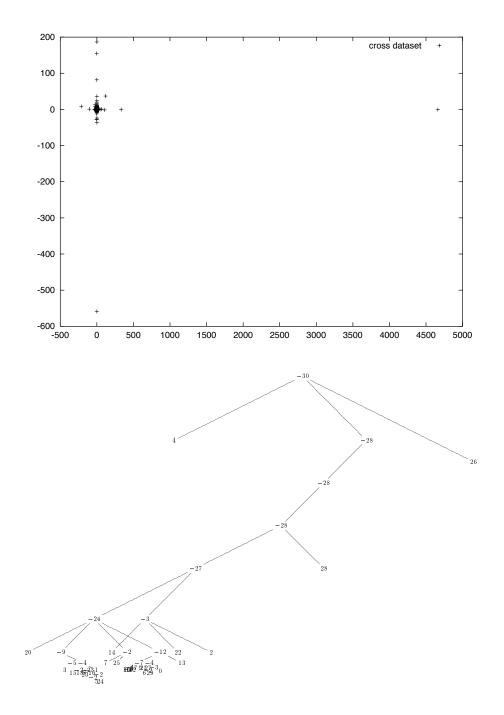

| 7.12 | Cross dataset for the Barnes-Hut application and its hierarchical rep-        |  |  |  |

|      | resentation. Positive numbers represents leafs while negative numbers         |  |  |  |

|      | represents the number of leafs dominated by the node                          |  |  |  |

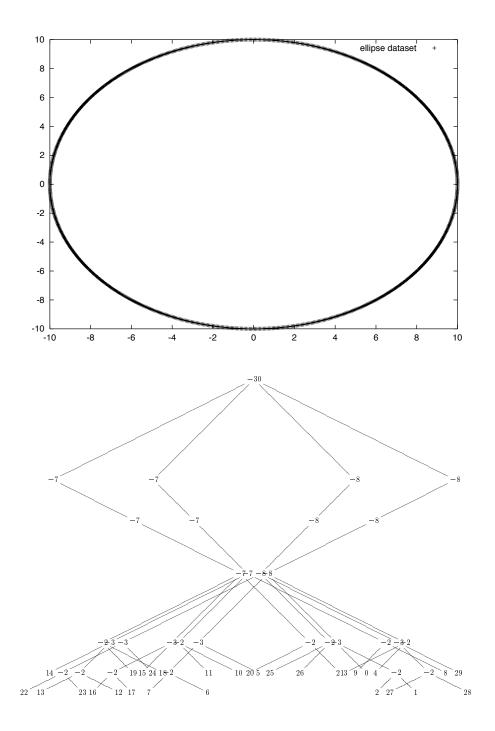

| 7.13 | 7.13 Ellipse dataset for the Barnes-Hut application and its hierarchical rep- |  |  |  |

|      | resentation. Positive numbers represents leafs while negative numbers         |  |  |  |

|      | represents the number of leafs dominated by the node. $\ldots$                |  |  |  |

# List of Tables

| 1.1               | Moore's Law                                                                                                                                                                                                                                                                                                       |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.2               | Semiconductor Industry Association (SIA) density forecast for logic (processor + cache) and DRAM [152]. Logic Cost-Perf. includes a little L1 cache, Logic High-Perf. includes large L1+L2+L3 caches 5                                                                                                            |

| 1.3               | Intel Pentium III and AMD Athlon: A lot of instruction level paral-<br>lelism and large caches                                                                                                                                                                                                                    |

| 2.1<br>2.2<br>2.3 | Concept recap: Owner computes rule                                                                                                                                                                                                                                                                                |

|                   | Figure 2.6                                                                                                                                                                                                                                                                                                        |

| 3.1<br>3.2<br>3.3 | Memory models supported by various processors and systems 94<br>Concepts recap: Dynamic scheduling and speculative execution 95<br>Concepts recap: Manager, owner, copy set, and migration mechanism 106                                                                                                          |

| $5.1 \\ 5.2$      | Type constructors for spread trees, spread arrays and shared regions. 134<br>Static and dynamic initializer for spread trees, spread arrays and<br>shared regions. $\mathcal{T}\langle \tau, k \rangle$ , $\mathcal{A}\langle \tau, k \rangle$ , $\mathcal{R}\langle \tau \rangle$ are type variables in abstract |

|                   | syntax                                                                                                                                                                                                                                                                                                            |

| $5.3 \\ 5.4$      | Primitives for spread trees SDTs                                                                                                                                                                                                                                                                                  |

| 5.5               | eskimo handlers                                                                                                                                                                                                                                                                                                   |

| <b>P</b> 1        |                                                                                                                                                                                                                                                                                                                   |

| 7.1               | Barnes-Hut performance (secs) on several ellipse and cross datasets<br>for Barnes-Hut application (sequential, MPI and eskimo) on a SMP<br>cluster (2-way 550MHz PIII)                                                                                                                                            |

| 7.2               | Barnes-Hut speedup on several ellipse and cross datasets for Barnes-<br>Hut application (sequential, MPI and eskimo) on a SMP cluster (2-                                                                                                                                                                         |

|                   | way 550MHz PIII)                                                                                                                                                                                                                                                                                                  |

| 7.3 | Barnes-Hut efficiency on several ellipse and cross datasets for Barnes- |

|-----|-------------------------------------------------------------------------|

|     | Hut application (sequential, MPI and eskimo) on a SMP cluster (2-       |

|     | way 550MHz PIII)                                                        |

# Chapter 1 Introduction

Information Technology advances in supercomputing, simulation, and networks are creating a new window into the natural world, making high end computational experimentation a vital tool for path-breaking scientific discovery.

Supercomputing is one of the foremost technologies in computing domain. We can see the imprint of this technology in many vital areas of scientific concern, such as forecasting global climate changes, monitoring nuclear reactors, enhancing automotive efficiency, modeling the evolution of galaxies, forecasting the flow of air over surface of vehicles and the damage due to impacts, and so forth.

In these areas, computational modeling is used to simulate physical phenomena that are impossible or very costly to observe through empirical means. Computational modeling allows in-depth analyses to be performed cheaply on hypothetical designs through computer simulation. In the coming years, computer simulation, spurred by technology changes already underway, can and should play an even greater rôle in providing solutions to our most challenging problems. However, a direct correspondence can be drawn between levels of computational performance and the problems that can be studied through simulation: each science and engineering application has a proper threshold of computing capacity (and cost) at which it becomes viable. And each era has its own Grand Challenge problems, i.e. problems that require a computing power threshold that falls far beyond the current availability.

Commercial and industrial computing has also come to rely on high performance architectures for its high end. Although for industrial needs the scale of computational performance is typically not as large as in scientific computing, they require a very aggressive development and deployment time for both hardware solutions and applications. In the past decade our group has been particularly active in transferring results from the research environment to the application marketplace. The pioneering work on P<sup>3</sup>L parallel language [27], its industrial deployment SkIE [29, 167], and lately on the ASSIST [169, 13, 12, 11] programming environment indeed take care of critical industrial requirements such as: rapid prototyping, performance portability, software reuse, integration and interoperability of parallel applications with the already developed standard tools.

The widespread diffusion of high performance computing depends also on its ability to satisfy the needs of industrial users, whose main goal is to exploit potentiality of parallel machines, in a more modest-scale with respect to scientific computing, but with a more aggressive requirement in time to development and deployment both for hardware and applications.

Advancements in several technologies over the past few years have had a major impact on the computing arena. Today's application professionals have far more computing power available to them, thanks to the fast-paced growth in hardware technology both in "raw technology performance" (e.g. clock cycle, transistor density) and in "architectural performance" (e.g. pipelining). In spite of this, the demand for performance, propelled by both challenging scientific and industrial problems, is still increasing. Even assuming a very optimistic pace of growth in processor performance, very large parallel architectures are needed to address current challenging scientific/industrial problems in a reasonable time-gap. The importance of parallelism meeting the application demand for ever greater performance can be brought into sharper focus by looking more closely at the advancements in the underlying technology and architecture: growth of the instruction level parallelism and processor level parallelism both in commodity and high-end computing marketplaces.

Moreover, the machine peak power is not the only issue. Lots of efforts has been made in the software side by the research community in order to tame parallel machine peak power and turn it into application performance. Our direct experience in the design of parallel compilers and software environments enforces this trend. Efficiently supporting challenging social/industrial applications, which algorithmic solutions are often irregular and dynamic (notably massive data mining, computational chemistry), requires both very high computational power and high flexibility of the programming model. In turn, this requires a powerful but clean computational model at the hardware/software boundary.

#### **1.1** Contributes and motivations of the thesis

This work originates from the wish to simplify the coding of irregular applications within our group programming environments. In these environments parallelism is exploited by composing "skeletons", i.e. parallelism exploitation patterns. From language viewpoint, a skeleton is a higher-order function that behaves as a pure function (no side-effects). Several real world, complex applications have been developed using these environments.

The skeletal approach has been proved to be effective, at least if application algorithms can be somehow expressed in terms of skeleton composition. However, in some cases our skeletal frameworks fail in providing the application programmer with convincing solutions both from ease of programming and performance viewpoints. Major lacks of expressivity have emerged in dynamic/irregular algorithms and applications that oddly access to large data sets. The first part of the thesis moves along this path (Section 2), and reports all attempts we made to improve the effectiveness of environments' compiler, static optimizer, and run-time support.

Stimulated by application requirements we eventually changed also the programming model, thus the role of skeletons in the language. In order to easily manage large data sets we designed a new environment (i.e. ASSIST) that explicitly admit a shared state among processing elements.

These research results as has been already presented in published papers. Some of those originated from the design, development and experimentation of software packages. In particular, I participated to the design or development of the following programming environments:

- SkIE (1998) programming environment and its compiler [7];

- FAN (2000), a functional skeletal parallel programming framework [18];

- Lithium (2001), a pure Java parallel programming environment [15, 16, 17];

- ASSIST (2002) programming environment [11, 12, 13];

also, I designed and developed the following programming platforms:

- Meta (1999) optimization tool and for skeleton-based languages [8, 9];

- Skel-BSP (2000), a skeletal language and its run-time on top of the Padeborn University BSP-library [9];

- eskimo (2002) language and its run-time support [10] (Chapters 4, 5 and 6).

All software packages except SkIE are available as open source.

The main goal of the thesis is to take a step further with respect to the achieved results. In particular we aim to defeat expressivity lacks emerged in skeletal languages approaching irregular problems and dealing with dynamic data structures. The basic idea consists in providing the application designer with a shared address space and a skeletal framework that enables and enforces the co-design of (shared) dynamic data structures and (parallel) algorithms. We shall go further in the discussion in Section 1.3.

At this aim, in the second part of the thesis (Chapters 4, 5 and 6) a new skeletal programming environment based on shared address programming is proposed (i.e. eskimo). The language is as an extension of a "host" language (i.e. the C language). eskimo is conceived to be a framework to experiment how to support dynamic data

structures in a skeletal framework. Its run-time support is based on a software distributed shared memory, and allows the programmer to freely access data items in the shared memory. eskimo is designed to match the hooks offered by ASSIST, thus to be experimented within. Notably eskimo is not yet another DSM, rather it relies on DSM already known technologies to experiment the co-design of dynamic data structures and parallel programming patterns enforcing locality in the distributed memory access.

eskimo has been designed and developed from scratch, and actually is a pretty young product. eskimo run-time support exploits multithreading, dynamic datadriven scheduling, and is very tolerant with respect to standard POSIX programming framework (notably, it does not use signal-handlers). It will be released as open source package.

In the next section we shall recap some technical background of the work. In Section 1.3 we shall return back on thesis contributes and motivations in the light of introduced concepts.

#### 1.2 Technical background

Dealing with sequential machines, we generally take programs for granted: the field is mature, and there is a large base of programs that can be viewed as fixed. We optimize the machine design against the requirements of these programs. Although we recognize that programmers might further optimize their code, we usually evaluate new designs without anticipating such software changes. Compilers may evolve along with architecture, but the source program is still treated as fixed. In parallel architecture, there is a much stronger and more dynamic interaction between the evolution of machine designs and that of parallel software. Since parallel computing is all about performance, programming tends to be oriented towards taking advantage of what machines provide.

In the next section we shall briefly analyze trends in parallel architectures and their building blocks, on this basis we shall choose a parallel architecture class, and we shall highlight what the peculiarities of machines in the class are. Along the discussion we shall put aside a number of findings, that eventually we shall elaborate to distill our wish list on the programming model, and on what are the issues it should cope with.

**VLSI evolution.** The VLSI technology trends may help us to understand what architectural directions may be adopted. Historically, Dynamic RAM (DRAM) has been recognized as the technology drivers for the whole VLSI industry. Prior to the early 1990s, logic (e.g. processor) technology was developed at slower pace than DRAM technology. During the last few years, the development rate of new technology.

**Moore's Law:** A historical observation by Intel executive, Gordon Moore, that the market demand (and semiconductor industry response) for functionality per chip (bits, transistors) doubles every 1.5 to 2 years. He also observed that MPU performance [clock frequency (MHz) x instructions per clock = MIPS] also doubles every 1.5 to 2 years. Although viewed by some as a "self-fulfilling" prophecy, "Moore's Law" has been a consistent macro trend, and a key indicator of successful leading-edge semiconductor products and companies for the past 30 years.

#### Table 1.1: Moore's Law

gies used to manufacture microprocessors has accelerated, closing the technology gap with DRAM. Currently, both DRAMs and microprocessors are increasing in functions per chip more than a factor of 30 per decade, accordingly with Moore's Law (see Table 1.1). As shown in Table 1.2, the Semiconductor Industry Association (SIA) foresees the same trend also for the next decade [152].

However, logic and DRAM technology, both under strong market pressure, have followed different evolutions: DRAM technology has moved towards the reduction of costs, the increase of storage room and the productivity of assembly lines, which are dominated by cell density and chip size. Microprocessor technology has also moved towards the reduction of costs, but with the additional target of maximizing the performance, which is dominated by the length of the transistor gate and by the number of interconnected layers.

The large availability of resources have allowed an ever increasing number of parallel functional units in microprocessor design leading an increasing number of instruction per clock cycle. This "architectural" improvement coupled with clock frequency improvement is leading microprocessors performance (ops/second) to increase by more than a factor of 15–30 per decade<sup>1</sup>. In the same time-gap, DRAM cycle times is improving much more slowly, roughly a factor of two per decade. Currently, hundreds to thousands clock cycles are needed to service an off-chip cache

| Year                           | 1999 | 2001 | 2003 | 2005 | 2008 | 2011 | 2014  |

|--------------------------------|------|------|------|------|------|------|-------|

| Logic Gate Length (nm)         | 180  | 150  | 120  | 100  | 45   | 30   | 20    |

| Logic Cost-Perf. (Mtrans/chip) | 24   | 48   | 95   | 190  | 539  | 1523 | 4308  |

| Logic High-Perf. (Mtrans/chip) | 110  | 220  | 441  | 882  | 2494 | 7053 | 19949 |

| DRAM (Gbits/chip)              | 1.07 | 2.15 | 4.29 | 8.59 | 24.3 | 68.7 | 194   |

<sup>1</sup>The factor is 100–200 if considered on the basis of floating point operations.

Table 1.2: Semiconductor Industry Association (SIA) density forecast for logic (processor + cache) and DRAM [152]. Logic Cost-Perf. includes a little L1 cache, Logic High-Perf. includes large L1+L2+L3 caches.

|                                   | Pentium III (600MHz) | Athlon (800MHz) |

|-----------------------------------|----------------------|-----------------|

| No. of transistor (L1 cache only) | $\sim 9.5 { m M}$    | $\sim 21 M$     |

| Operation per clock cycle         | 5                    | 9               |

| Integer+Floating pipelines        | 2+1                  | 3+3             |

| L1 cache size                     | 32KB                 | 128KB           |

| L2 cache size (up to)             | 2MB                  | 8MB             |

| cache coherence support           | MESI                 | MOESI/MESI      |

| multiprocessing support           | shared bus           | point-to-point  |

Pentium III (600MHz) Athlon (800MHz)

Table 1.3: Intel Pentium III and AMD Athlon: A lot of instruction level parallelism and large caches.

miss in an uniprocessor box; such gap between processor speed and memory speed is likely to continue to widen in the coming years.

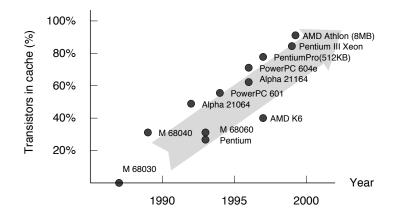

Together with parallelism, the other way to translate such large volume of transistor into performance is locality. Caches, through locality, help to maintain data close to processor, thus reducing the frequency of accesses at deeper levels of the storage hierarchy. Indeed, as we can see in Figure 1.1, since caches migrated on chip in the mid-1980s, the fraction of the transistor on commercial processor that are devoted to caches has risen steadily. As a matter of fact, today's microprocessors are mostly memory.

Let us make concrete our arguments with a couple of examples: The Intel Pentium III and the AMD Athlon. These are last generation commodity processors with a good cost-performance trade-off (not high-performance), Table 1.3 briefly describes their features [2]:

It is worth pointing out that both processors, in order to issue up to 5–9 instruction per clock cycle, internally exploit at least three different paradigms of parallelism: pipeline, functional units replication and specialization. Both processors support also up to 2–8 MBytes of L2 cache. In addition, both processors already contain hooks (such as snoopy buses) to work in a cache-coherent shared memory multiprocessor framework.

Let us put aside a first finding: Modern microprocessors are complex and exploit substantial instruction level parallelism. Large caches are used to provide a great deal of local storage in order to satisfy bandwidth requirement of processor functional units with a reasonable latency. Moreover, in order to stay on the processor performance growth trend, the increase in the ratio of memory access time to processor cycle time will require that the processors employ better latency avoidance and *latency tolerance* techniques. In addition, the increase in processor instruction rates, due to the combination of cycle time and parallelism, will demand that the *bandwidth* delivered by the memory increases.

Figure 1.1: Fraction of transistors on microprocessor chip devoted to caches.

**Parallel architectures.** Current trends would suggest that, simply riding the commodity growth curve, we could look towards achieving petaflops-scale peak performance in a decade, or even earlier if the scale of parallelism is increased. It is less clear what level of communication performance these machines will provide.

As discussed, modern commodity microprocessors already includes hooks for implementing multiprocessor systems. Nevertheless, a large multiprocessor system needs a pretty efficient memory sub-system to feed many processors. Currently, the design and the implementation of memory sub-system is the main cost of large multiprocessors. As a matter of fact, the better price/performance trade-off is reached in low-scale multiprocessors. They may be in turn put together using high-speed networks, in facts turning every LAN into a potential parallel machine. These machines (namely Beowulf class clusters or simply clusters) are gaining more and more interest as low-cost parallel architectures, and actually more positions in the TOP500 [164] parallel architecture list. Currently ASCI clusters and SMP clusters occupy 112 positions of the list. Although these parallel machines cannot be classified as low-cost Beowulf clusters – mainly due to the adoption of high-end interconnection networks and to the number of nodes used – the architectural trend is clear [70].

In summary, microprocessors in a Beowulf machine may exchange data one each other using different means: the shared memory (within the single node) and the network (among the nodes). In general, these means support different data exchange protocols in native manner, i.e. a shared address space and message passing. Nevertheless, as we shall see in the next section, we can simulate one programming model using the other in order to supply the programmer with an uniform programming model. Therefore, let us assume a Beowulf machine as a big multiprocessor exploiting an extended (multi-level and distributed) memory hierarchy.

The two key factors in VLSI evolution discussed in previous section (i.e. the increase of single chip performance as well as on-chip storage capacity), and in parallel machines evolution (Beowulf) will cause the storage hierarchy to continue

becoming deeper and more complex.

The trend towards deeper hierarchies presents a problem for parallel architectures since communication, by its very nature, involves crossing out the lowest level of the memory hierarchy on the node, leading a growth of the actual latency on operations that crosses the processor chip boundary. The problem is further exacerbated in Beowulf class machines that in general exhibit a heavily unbalanced communication bandwidth/computing power ratio.

Let us put aside our second finding: memory systems in parallel machines are constructed as a hierarchy of increasingly larger and slower memories: on an average, a large hierarchical memory is fast, as long as as the references exhibit good locality.

#### **1.2.1** Parallel architectures: programming model

Message passing and shared address space represent two clearly distinct programming models, each of them providing a well-defined paradigm for sharing, communication and synchronization. Historically, parallel architectures have been designed in such a way to naturally support a specific programming model.

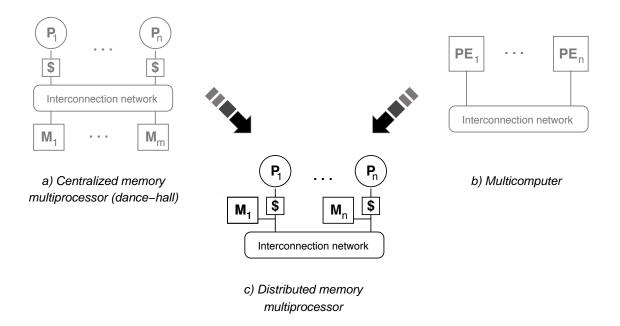

A shared memory system makes a global physical memory equally accessible to all processors. These systems naturally offer a shared address space, i.e. a convenient programming model enabling simple data sharing through a uniform mechanism of reading and writing shared structures in the common memory (see Figure 1.2 a). However, such systems typically suffer from increased contention and latency in accessing common shared memory, which in general limits the scalability compared to other memory organizations.

Multicomputers consist of multiple independent processing nodes with local memory modules, connected by a general interconnection network. The scalable nature of the distributed memory makes them scalable and very powerful in computing peak power. The natural programming model is message passing, that is widely considered exacting from programmer viewpoint because of the explicit data distribution of data structures in the distributed memory (see Figure 1.2 b).

The evolution of the hardware and software has blurred the clear boundary between the multiprocessor and multicomputer machine organizations. The convergence has been driven by many factors. One is clearly that all of the approaches have common requirements. They require a fast, low latency and robust interconnect. They all benefit from hiding as much of the communication cost as possible: the goal is often pursed by equipping commodity processors (reducing also development cost and time) with specialized *communication co-processors* (e.g. smart communication boards like Myrinet and SCI).

On the software side, the convergence of multiprocessor and multicomputer machine schemes is enforced by the possibility of simulating one programming model using the other, and vice versa.

Figure 1.2: Typical parallel machine schemes.

- Classical message passing operations (send/receive) may be supported on shared memory machines through shared buffer storage. Send involves writing data into the buffer, while receive involves reading the data from the shared buffer. Flags into the buffer are used to enforce mutual exclusion (locks) and to indicate a category of events such as message arrival.

- User processes on a message passing machine may construct a global address space by carrying along pointers specifying the process and the local virtual address in that process. A logical read is implemented by sending a request to the process containing the object and receiving an answer. The read/write simulation may be hidden from the user by carrying out library or compiler generated code. As we will see later in Chapter 3, a shared virtual address space can be established at the page level. Since only local pages are directly accessible with such machines, pages instead of single words or cache lines are actually moved/copied among processing elements, in fact coarsening the granularity of messages.

The 1990s have exhibited the beginning of a convergence among these various factions. Propelled by both economical and technical issues, shared memory and multicomputer schemes have converged towards a common organization, represented by a collection of complete computers, augmented by a communication co-processor connecting each node to a scalable communication network. Focusing on the memory organization, we call them *distributed memory multiprocessors* (see Figure 1.2 c). Such systems, depending on co-processor functionality, may act as multiprocessor or

multicomputer, thus providing a shared address space or a message passing model at the assembler level [65]. Such co-processor may also be implemented in software. A software DSM may be used to provide a multicomputer with a shared address space; therefore it may turn a Beowulf class cluster into a multiprocessor. Since (Beowulf + software DSM) multiprocessors are both cheap and flexible, they are quite good platform to experiment solutions at hardware/software boundary like mapping, scheduling, caching strategies and memory consistency models.

Making the memory hierarchy efficient. As we shall see in Chapter 3, many methods have been proposed to alleviate latency/bandwidth problems in multiprocessor architectures. Almost all approaches rely on the following findings:

- 1. reduce communication and synchronization cost as seen by the processor;

- 2. reduce serialization at shared resources, reduce communication volume;

- 3. reduce non-inherent communication via data locality;

Almost all approaches to face the first issue consist in hiding long latency memory communications by overlapping them with computation or other communications. Actually, there are many ways to implement, both in hardware and software, this basic idea: prefetching, multithreading, non-blocking transactions and so forth. Some of these methods are currently supported in shipped multiprocessor and parallel applications with various mileage. However, many of the latency tolerance techniques increase the absolute amount of memory traffic by fetching more data than are needed, also creating contention in the memory system [46].

Relaxed memory consistency models essentially face up the first and the second issues by enabling the hiding of remote memory access latency and the reduction of coherence-oriented handshakes. The research community has proposed a plethora of relaxed memory consistency in the past decade, which are collected and discussed in Section 3.

Third issue is probably the foremost from our viewpoint. Memory systems in modern multiprocessor are constructed as a hierarchy of increasingly larger and slower memories: on an average, a large hierarchical memory is fast, as long as as the references exhibit good locality. This is particularly true in (Beowulf + software DSM) machines, where at least one layer of virtual memory is implemented through network transactions. At this end, software DSMs rely on relaxed memory consistency in order to reduce communication frequency and volume.

#### 1.2.2 High-level parallel programming

Although building parallel computers has become easier, programming parallel computers can still be quite difficult. Most application programs are currently being written at the low level of C or Fortran, combined with a communication library like MPI; moreover, they are often tuned towards one specific machine configuration. Since parallel computers are typically replaced within five years, parallel programs which live longer have to be re-tuned or redesigned. In addition, programming at this low level of abstraction is cumbersome and error-prone.

In sequential programming, coding for a specific machine also prevailed three decades ago. The software engineering solution to overcome it was to introduce levels of abstraction, effectively yielding a tree of refinements, from the problem specification to alternative target programs [137]. The derivation of a target program then follows a path down this tree. The transition from one node to the next can be described formally by a semantics-preserving program transformation or refinement. Conceptually, porting a program to a different machine configuration means backtracking to a previous node on the path and then following another path to a different target program.

In the parallel setting, high-level programming constructs and a refinement framework for them are necessary due to the inherent difficulties in maintaining the portability of low-level parallelism [61]. In the 1990s, the "skeletons" research community [59] has been working on high-level languages and methods for parallel programming [27, 29, 17, 18, 45, 77, 98]. Skeletons are higher-order functions which can be evaluated efficiently in parallel. They specify abstractly common patterns of parallelism which can be used as program building blocks. Typical skeletons model data and task parallel paradigms (see Chapter 2) as for example the pipeline, task farm, reduction, scan and "sequential". Sequential skeleton is a final skeleton embodying sequential chunks of user code. Such code is guaranteed to be executed in a sequential fashion. Sequential skeleton enables the reuse of already developed (and tested) application source code and libraries.

In the past decade our research group has been active in experimenting new technologies for high-level parallel programming. These are mainly targeted to simplify programming by raising the level of abstraction; to enhance portability by absolving the programmer of responsibility for detailed realization of the underlying parallel paradigms; to improve performance by providing access to carefully optimized implementations of the paradigms. These technologies have been used to design programming environments and languages and to implement their compilers. Skeletons have been present all along in programming environments, even if their role has been permanently changing (see Section 2.1). Cole's skeletons represent parallelism exploitation patterns that can be used (instantiated) to model common parallel applications. Later, different authors acknowledge that skeletons can be used as constructs of an explicitly parallel programming language, actually as the only way to express parallel computations in these languages [76, 27]. Recently, the skeleton concept evolved, and became the coordination layer of structured parallel programming environments [26, 29, 147, 169].

Current skeleton-based systems typically provide the user with a collection of high-level skeletal constructs and with a compiler for translating skeleton programs into low-level target code [27, 56, 138, 153]. Alternatively, high-level skeletal con-

structs are used to equip a sequential or already parallel language, in facts extending it; in this case skeletons' implementation code is collected in libraries [17, 72, 75, 120]. Typically, skeletons carry a large amount of information on program interaction structure, which can be used by the compiler/run-time support to exploit efficient code on different target machines. Compiler approaches mostly rely on static optimization of the generated code, while libraries follow a more dynamical way.

Static versus dynamic run-time support. It is an old story, and clearly we have nothing to add up to the general question. Let us restrict the context to skeleton-based languages.

Early approaches to skeletons implementation has followed the static way. Such approaches were based on the concept of *implementation template*, i.e. a parametric processes network. Given a program, i.e. a particular nesting of skeletons, the compiler turns it into a processes network. Together with processes network a mapping plan is generated. At the run time a program loader places processes on parallel machine nodes according to the mapping plan. Each process of the network has a fixed role, that is established by the compiler.

The basic idea under the approach is that the compiler may "compositionally" build the final processes network by associating a processes network (taken from a library) to each skeleton. In case a skeleton is nested into another the implementation template of the inner skeleton is somehow merged with the outer one. During the merge process several optimizations on the process network may be performed, basically by merging some of adjacent processes in a single one. Moreover, the processes network may be targeted to a given physical network topology. Eventually, a (flat) processes network is generated. This network is still parametric and may be instanced with typical architectural constants as for example computation and communication grain.

However, high performance is only reached if a composition of skeletons is found which matches both the application and the target machine requirements. One possible way to address the problem is to integrate skeletons with refinement framework. The basic idea follows the mainstream of code optimization for sequential languages: the skeleton-based program is optimized by means of source-to-source semantic-preserving refinements targeted to obtain a "better" source code. Furthermore, due to the fact that the skeletons have a clear functional and parallel semantics, different rewriting techniques have been developed that allow skeleton programs to be transformed/rewritten into equivalent ones achieving different performances when implemented on the target architecture [38, 94]. One further concept, not as crucial in sequential programming, has to be added: the program refinements must be adorned with a cost model, since "efficiency" is the main – often the single – reason for using parallelism. A cost model actually formalizes the comparison between two (semantically-equivalent) source codes. In the past decade this "efficiency" was primarily interpreted as "speedup". Nowadays – particularly in a distributed parallelism scenario – it assumes a larger meaning involving efficient use memory room and network bandwidth, etc.

Several cost models have been developed [158, 159, 14, 172] and have confirmed that porting a parallel program from one machine configuration to another may dramatically alter its performance [94]. Therefore, program design tools must apply transformations based on performance predictions made in a cost model.

At this end we designed and developed the Meta tool, i.e. an optimization tool for skeleton-based programs. Given a skeleton-based language and a set of semanticpreserving transformation rules, the tool locates applicable transformations and provides performance estimates, thereby helping the programmer in navigating through the program refinement space. Meta is described is Section 2.2. It has been used as optimization engine of several skeleton-based programming frameworks [18, 8, 9]. Meta has proved to be an effective optimization tool, provided that a rich set of rewriting rules exists and is equipped with a careful cost model. The cost model is crucial in order to make correct decision both during the compiling and optimization process.

Unfortunately, these assumptions have been proved hardly satisfied in practice. It is worth highlighting two major problems in that:

- It is pretty difficult to make assumptions about the computational cost of sequential parts of the application (i.e. parts within sequential skeletons). They may call functions that are not available in the source form; and even in case all sequential source code is available, its correct cost profiling is possible in limited cases only, i.e. cases in which sequential code behaves in a very predictable manner and its cost does not (heavily) depend on input data.

- Defining a compositional cost model for a generic target platform is almost impossible. One possible way to avoid the problem consists in constraining how the target platform behaves in respect of synchronizations. For example, fairly good predictions can be figured out assuming a BSP model [165] (see also Section 2.2.4 [9, 172]). However such constraints prevent the both runtime support designer and application programmer to exploit all performance capabilities of current technology.

Indeed, recently more dynamical ways to support skeletons have been explored. These are aimed at defeating the disadvantages relative to the need of a cost model both in compiling and optimizing a skeleton program. It has been observed that skeletons naturally impose a data flow relationship among the computations performed by the different processes in the process graph implementing the skeleton program on the target machine. Therefore it is possible to derive a graph of macro data flow instructions from the skeleton code in such a way that:

• each sequential portion of code in the skeleton program denotes a macro data flow instruction;

• and the parameter passing mechanism used in the skeleton program defines the arcs between such instructions.

That graph can be used to execute the parallel application by making each processing element in the target machine to behave as a data flow interpreter of the instructions of the graph [70]. The mechanism exploits some ideas from previous work on macro data flow developed in rather different contexts [114, 135].

The macro data flow implementation technique has been adopted in the run-time support of the Lithium parallel programming environment (described in Section 2.3 [17]) and in the SKIPPER project [153]. Macro data flow has demonstrated to be effective in design of the run-time support. The universality of macro data flow interpreter greatly simplifies the mapping and scheduling problems in respect of static approach. In addition, we demonstrated that some of the optimization techniques developed for the static case are still applicable and useful in the new approach (as for example the "normal form reduction" [15]). Overall, the macro data flow run-time support has demonstrated to overcome many of the problems of fully static skeletons' run-time support (introducing a limited overhead).