Utilizzando la metodologia del corso, proviamo ad implementare una rete di Mealy che implementi l'automa in Figura

A questo automa corrispondono le seguenti funzioni di transizione di stato e delle uscite:

Dunque possiamo implementare la corrispondente rete di Mealy come segue.

module sigma(output s1, input s, input x); assign #2 s1 = ((~s) && (x)) || (s && (~x)); endmodule

module omega(output z, input s, input x); assign #1 z = ((~s) && (~x)); endmodule

module registro(out, in, beta, clock); output out; input in; input beta; input clock; reg r; initial begin r = 1'b0; end always @ (posedge clock) begin if(beta==1) #1 r = in; // ritardo di un tp per la scrittura del registro end assign out = r; endmodule

Con i componenti descritti in precedenza, possiamo desrivere la rete di Mealy come segue:

module mealy(output z, input x, input clock); wire r2so; wire s2r; registro registrostato(r2so, s2r, 1'b1, clock); sigma rete_sigma(s2r,r2so,x); omega rete_omega(z, r2so,x); endmodule

I diversi componenti utilizzati sono stati testati ognuno con il proprio test bech.

module prova_omega(); reg x; reg r; wire z; omega o(z,r,x); initial begin $dumpfile("omega.vlc"); $dumpvars; x = 0; r = 0; #10 x = 1; #10 r = 0; #10 x = 1; #10 $finish; end endmodule

module prova_sigma(); reg x; reg r; wire z; sigma s(z,r,x); initial begin $dumpfile("sigma.vlc"); $dumpvars; x = 0; r = 0; #10 x = 1; #10 r = 0; #10 x = 1; #10 $finish; end endmodule

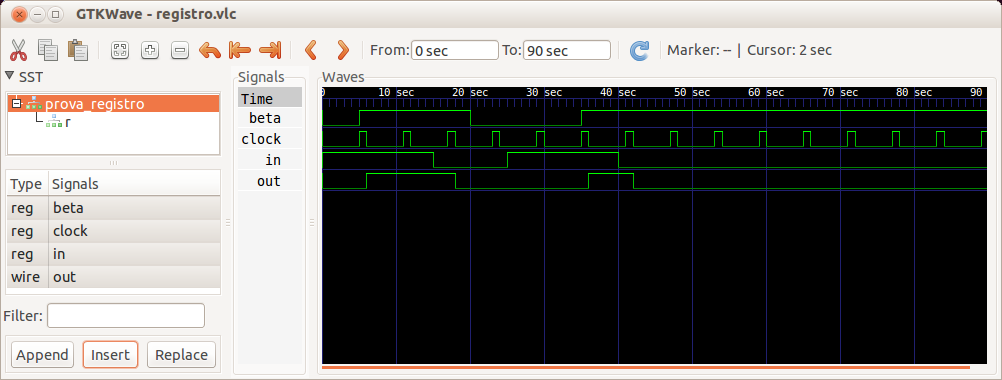

module prova_registro(); reg in; reg beta; wire out; reg clock; registro r(out, in, beta, clock); always begin #5 clock = ~clock; #1 clock = ~clock; end initial begin $dumpfile("registro.vlc"); $dumpvars; clock = 0; in = 1; beta = 0; #5 beta = 1; #10 in = 0; #5 beta = 0; #5 in = 1; #10 beta = 1; #5 in = 0; #50 $finish; end endmodule

module prova_mealy(); wire z; reg x; reg clock; mealy reteDiMealy(z, x, clock); always begin if(clock==0) #2 clock=1; else #1 clock=0; end initial begin $dumpfile("mealy.vlc"); $dumpvars; x = 0; #10 x = 1; #10 x = 0; #10 x = 1; #10 $finish; end endmodule

Il registro viene scritto solo alla fine del ciclo di clock, quando beta vale 1, come ci si aspettava. Notare che il registro descrive il passaggio dell'input sull'output del registro come un evento che avviene quando il segnale di clock va alto e che dura un tp (ritardo #1) (vedi sorgente reg.vl)

Nello stato iniziale 0 (out nel grafico) ad ogni ingresso x=0 l'uscita è 1 e si rimane nello stato 0. Quando arriva un ingresso a 1, l'uscita va a zero e si passa nello stato 1 (si notino le temporizzazioni).